MANUEL HARDWARE

DES CARTES

MCXCompactPCI/570-2

MCXCompactPCI/570-4

MCXCompactPCI/570-2-R

MCXCompactPCI/570-4-R

WAN-HDLC/4C

# MANUEL HARDWARE DES CARTES MCXCPCI/570-2, MCXCPCI/570-4, MCXCPCI/570-2-R, MCXCPCI/570-4-R WAN-HDLC/4C

#### **COPYRIGHT (©) ACKSYS 1999 - 2001**

Ce document contient des informations qui sont protégées par Copyright.

Tout ou partie du présent document ne pourra être reproduit, transcrit, stocké dans n'importe quel système informatique ou autre, traduit dans n'importe quelle langue et n'importe quel langage informatique sans le consentement préalable et écrit de *ACKSYS*, 3 & 5 rue du Stade, BP 4580, 78302 POISSY CEDEX.

# **MARQUES DEPOSEES** ®

- ACKSYS est une marque déposée de ACKSYS.

- MS-DOS, Windows sont des marques déposées de MICROSOFT.

#### **NOTICE**

ACKSYS ® ne garantit en aucune façon le contenu du présent document et dégage son entière responsabilité quant à la rentabilité et la conformité du matériel aux besoins de l'utilisateur.

ACKSYS ® ne pourra en aucun cas être tenue pour responsable des erreurs éventuellement contenues dans ce document, ni des dommages quelle qu'en soit leur importance, du fait de la fourniture, du fonctionnement ou de l'utilisation du matériel.

ACKSYS ® se réserve le droit de réviser périodiquement ce document, ou d'en changer le contenu, sans aucune obligation pour ACKSYS ® d'en aviser qui que ce soit.

Société ACKSYS 3 & 5 rue du Stade BP 4580 78302 POISSY CEDEX

Téléphone

: 01 39 11 62 81

Télécopie

: 01 39 11 47 96

Web

: www.acksys.fr

# TABLE DES MATIERES

| I.    | LES CARTES MCXCPCI/570-2, MCXCPCI/570-4, WAN-HDLC/40           | С,                |

|-------|----------------------------------------------------------------|-------------------|

|       | MCXCPCI/570-2-R, MCXCPCI/570-4-R                               | I-1               |

| I.1   | Présentation                                                   | I-1               |

| I.2   | LES DIFFÉRENTS MODES D'UTILISATION                             |                   |

| I.2   |                                                                |                   |

| I.2   | 2.2 Le mode MCXDOS                                             |                   |

| I.2   | 2.3 Le mode stand-alone                                        | I-4               |

| I.3   | GARANTIE                                                       | I-5               |

| II.   | LA CARTE MERE MCXCPCI/0                                        | II-1              |

| II.1  | SYNOPTIQUE                                                     | II-1              |

| II.2  | CONFIGURATION                                                  | II-2              |

| II.3  | DÉMARRAGE DE LA CARTE                                          | II-3              |

| II.4  | HOT SWAP                                                       | II-5              |

| III.  | LES EXTENSIONS PCB570-2, PCB570-4, PCB570-4P, PCB570-2         | R, PCB570-4RIII-1 |

| III.1 | SYNOPTIQUE DE L'EXTENSION PCB570-2                             | III-2             |

| III.2 |                                                                |                   |

| III   | I.2.1 Le boîtier de connexion 570-BP                           |                   |

| III.3 | SYNOPTIQUE DE L'EXTENSION PCB570-4P                            | III-5             |

| III   | L3.1 Le câble de répartition 4P570M25                          | III-6             |

| III.4 | SYNOPTIQUE DE L'EXTENSION PCB570-2R                            | III-7             |

| III.5 | SYNOPTIQUE DE L'EXTENSION PCB570-4R                            | III-8             |

| III   | L5.1 La carte REAR I/O CPCIRIO2                                | III-9             |

| III.6 | CONFIGURATION CARTES PCB570-X                                  | III-10            |

| III.7 | ATTRIBUTION DES SIGNAUX SUR LES CONNECTEURS                    | III-12            |

| III   | I.7.1 Extension PCB570-2                                       |                   |

| III   | I.7.2 Extensions PCB570-4                                      |                   |

|       | I.7.3 Extensions PCB570-4P                                     |                   |

| III   | I.7.4 La carte REAR I/O pour extensions PCB570-2R et PCB470-4R | III-20            |

| ANN   | <u>NEXES</u>                                                   |                   |

| Ann   | NEXE ${f A}:{f Pour}$ ECRIRE UN PILOTE DE PERIPHERIQUE         | A-1               |

| Ann   | IEXE B: POUR PROGRAMMER DANS LA CARTE                          | B-1               |

| Ann   | JEXE C · FICHE ERREUR                                          | C-1               |

# I. LES CARTES MCXCPCI/570-2, MCXCPCI/570-4, WAN-HDLC/4C, MCXCPCI/570-2-R, MCXCPCI/570-4-R

#### I.1 PRESENTATION

Vous venez de faire l'acquisition d'une carte de communication intelligente de la gamme MCXCPCI format CPCI 6 U Hot Swap, et nous vous en remercions.

Les cartes de cette gamme ont été étudiées pour être compatibles avec toutes les machines disposant d'un bus CPCI 5V conforme à la norme CompactPCI Specification PICMG 2.0 et CompactPCI Hot Swap specification PICMG 2.1.

L'objet de cette documentation est de fournir les caractéristiques techniques des cartes MCXCPCI/570-x(-R) et WAN-HDLC/4C.

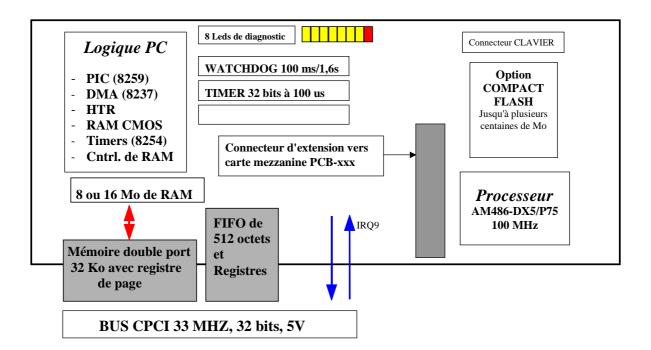

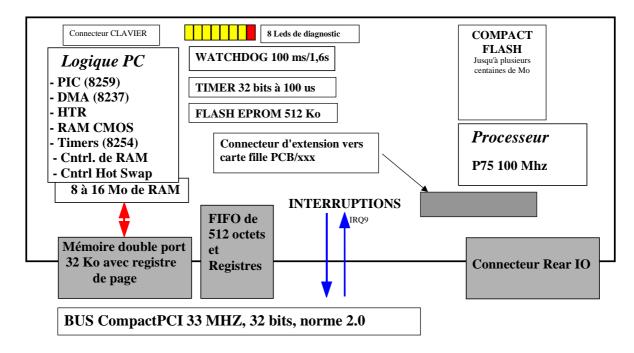

Les cartes MCXCPCI/570-x(-R) et WAN-HDLC/4C ont une architecture semblable à celle d'un PC AT muni d'un microprocesseur 486. Ces cartes disposent donc de leur propre microprocesseur (Pentium 75 100 MHz) pour assurer la gestion des lignes de communication. Elles disposent d'une mémoire de 8 Mo extensible à 16 Mo, d'un «watchdog» matériel, d'un contrôleur clavier, d'une EEPROM de 512 Ko contenant un BIOS compatible PC et d'un support pour une carte Compact FLASH type 1.

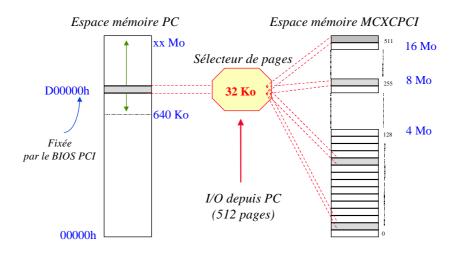

La communication entre la carte et la machine s'effectue par l'intermédiaire d'une mémoire de 32 Ko à double accès, le réglage des conflits étant assuré par la carte elle-même.

Cette carte offre 2 ou 4 voies série synchrones ou asynchrones RS232, RS422, RS485, RS449, V35, V36, EIA530(-A) hauts débits. Les cartes MCXCPCI/570-2, MCXCPCI/570-4, WAN-HDLC/4C, MCXCPCI/570-2-R et MCXCPCI/570-4-R sont respectivement construites à partir de la carte mère MCXCPCI/0 et

- D'une carte mezzanine PCB570-2

- D'une carte mezzanine PCB570-4

- D'une carte mezzanine PCB570-4P

- D'une carte mezzanine PCB570-2R et d'une carte Rear I/O CPCIRIO2

- D'une carte mezzanine PCB570-4R et d'une carte Rear I/O CPCIRIO2

#### I.2 LES DIFFERENTS MODES D'UTILISATION

La carte propose différents modes d'utilisation programmable via les cavaliers JP2.

| JP2       |           | Mode              |  |

|-----------|-----------|-------------------|--|

| 2-3 fermé | 5-6 fermé | Firmware          |  |

| 1-2 fermé | 5-6 fermé | Stand Alone       |  |

| 2-3 fermé | 4-5 fermé | Réservé<br>ACKSYS |  |

| 1-2 fermé | 4-5 fermé | MCXDOS            |  |

# Le mode BUILT-IN-FIRMWARE qui offre

- L'accès aux ports de communications en mode asynchrone ou synchrone depuis le P.C. sans programmation dans la carte.

- Un système de programmation de la FLASH EPROM pour mise à jour du firmware embarqué ACKSYS.

- Un système de téléchargement d'applications clients au format MCS-86.

# Le mode MCXDOS qui permet

Le développement et l'exploitations d'applications clients embarquées dans la carte. Les applications embarquées DOS peuvent être chargées dynamiquement depuis le P.C, les autres applications nécessitent l'utilisation d'un disque compact FLASH.

## Le mode STAND ALONE qui permet

L'exécution par la carte, d'applications embarquées dans un disque compact flash, de façon autonome sans intervention du P.C. Ce mode est typiquement utilisé lorsque la carte est montée dans un RACK.

#### I.2.1 Le mode « Built-In Firmware »

Le mode de programmation « Built-In Firmware » permet d'exploiter la carte depuis le P.C. en s'appuyant sur les fonctionnalités du firmware ACKSYS intégré dans la flash Eprom de la carte. Pour les systèmes d'exploitation les plus courants, ACKSYS fournit un pilote de périphérique s'exécutant sur le P.C hôte, offrant à votre applicatif P.C. une interface conforme au système d'exploitation P.C., masquant ainsi tous les détails du dialogue P.C carte implémenté dans le firmware.

Deux firmware ACKSYS sont disponibles :

- Le firmware « Logiciel de base », embarqué en standard sur toutes les cartes de la gamme MCXCPCI

- Le firmware « logiciel multiprotocole », embarqué en standard sur les cartes MCXCPCI/570-x(-R) et WAN-HDLC/4C, optionnel sur les cartes MCXCPCI/S et MCXCPCI/BP-X et non disponible pour la carte MCXCPCI/U-X et MCXCPCI/M128F

Les fonctionnalités offertes, avec le FIRMWARE LOGICIEL DE BASE sont les suivantes :

- Accès aux ports de communications en mode asynchrone, limité aux cartes MCXCPCI/S et MCXCPCI/BP-X

- Système de programmation de la FLASH EPROM pour mise à jour du firmware, disponible sur toutes les cartes de la gamme MCXCPCI

- Système de téléchargement de fichiers au format MCS-86, disponible sur toutes les cartes de la gamme MCXCPCI

Les fonctionnalités offertes, avec le FIRMWARE LOGICIEL MULTIPROTOCOLE sont les suivantes :

- Accès aux ports de communications en mode asynchrone et synchrone, excepté la carte MCXCPCI/U-X et MCXCPCI/M128.

Notez que toutes ces fonctionnalités sont aussi dépendantes du pilote de périphérique ACKSYS s'exécutant sur le P.C hôte. Autrement dit, il est conseillé de consulter la documentation s'y rapportant pour connaître les services supportés.

#### I.2.2 Le mode MCXDOS

Ce mode permet le **développement et l'exploitation d'applications embarquées** s'exécutant sous un système d'exploitation de votre choix, dans le mesure où il ne nécessite ni écran, ni intervention clavier/souris pour démarrer l'application.

#### LE DEVELOPPEMENT D'APPLICATIONS,

DANS L'ENVIRONNEMENT DOS COTE CARTE,

DANS L'ENVIRONNEMENT DOS, WINDOWS 9X COTE P.C.,

nécessite le kit d'aide au développement MCXDOS.

Les outils de développement restent les outils standards du marché.

En phase d'exploitation dans ces environnements, l'application embarquée sera chargée depuis le P.C grâce au logiciel AUTOMCX<sup>1</sup>. Notez que le logiciel AUTOMCX existe aussi pour le système d'exploitation Windows NT/3.51/2000, permettant ainsi d'exploiter la carte depuis cet environnement P.C.

# LE DEVELOPPEMENT D'APPLICATIONS DANS DES ENVIRONNEMENTS DIFFERENTS, nécessitent les fournitures suivantes :

Une carte compact FLASH pour stocker le système d'exploitation côté carte Un clavier connecté à la carte

Le logiciel MCXSPY (Emulation écran VGA en mode texte de la carte sur le P.C) Les outils de développement restent les outils standards du marché.

Il deviendra ainsi possible, par exemple de développer depuis un P.C sous Windows NT une application QNX dans la carte avec les outils de développement les plus performants. Attention l'environnement côté carte est restreint aux systèmes d'exploitations non graphiques et l'environnement côté P.C limité aujourd'hui à DOS, Windows 95/98, Windows NT/2000 & QNX.

#### I.2.3 Le mode stand-alone

Dans ce mode, la carte démarre sur le disque compact FLASH pour ensuite exécuter l'application embarquée. C'est donc un mode d'exploitation de la carte, et non de développement.

<sup>&</sup>lt;sup>1</sup> Intégré dans le kit MCXDOS

#### I.3 GARANTIE

La période de garantie est définie par nos conditions générales de garantie c'est-à-dire :

Garantie de 5 ans pièces<sup>1</sup> et main-d'œuvre contre tout vice de fabrication ou de fonctionnement à l'exception des pannes engendrées par une utilisation non conforme ou bien par l'action excessive d'un agent ou d'une circonstance naturelle.

Les réparations sous garantie sont effectuées en nos locaux dans un délai moyen de cinq jours ouvrés.

#### **AVERTISSEMENT**

- ♦ Afin d'assurer un fonctionnement correct de la carte, vérifiez que la batterie est correctement connectée.

- ♦ Le courant électrique provenant de l'alimentation, du téléphone et des câbles de transmission, peut présenter un danger.

- Connectez et déconnectez les câbles uniquement lorsque la machine dans laquelle est installée votre carte est hors tension.

- Ne touchez pas aux câbles pendant un orage.

# DANGER

# NE JAMAIS BRANCHER OU DEBRANCHER LES CONNECTEURS LORSQUE LA MACHINE EST SOUS TENSION

Les pannes engendrées par une manipulation répétée des connecteurs SUB-D avec la machine sous tension sont fréquentes et détruisent le plus souvent les amplificateurs de ligne.

La plupart des pannes sont facilement évitables à condition de respecter la règle énoncée cidessus.

#### **RESPECTEZ LA!**

\_

<sup>&</sup>lt;sup>1</sup> A l'exception de la batterie lithium qui n'est pas garantie.

| <u>I-6</u> | LES CARTES MCXCPCI/570-2, MCXCPCI/570-4, WAN-HDLC/4C                         |

|------------|------------------------------------------------------------------------------|

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

|            |                                                                              |

| ) /        | VADE DES CARRES MOVODOUEZO V. VERSIONER ANGAIGE NOVEMBRE 2001. REVISION A 01 |

# II. LA CARTE MERE MCXCPCI/0

La carte doit impérativement être installée dans un emplacement CPCI 6U de la machine, conforme à la norme CompactPCI Specification PICMG 2.0.

# II.1 SYNOPTIQUE

La configuration hardware de la carte (les adresses de la mémoire double port, les adresses des registres d'I/O et l'interruption de la carte MCXCPCI/O vers PC) est fixée par le BIOS PCI du PC au moment du démarrage du PC. Attention, cette configuration peut changer si vous déplacez la carte dans un autre slot CPCI. Notez qu'il est possible avec certains PC de fixer l'interruption utilisée par la carte.

# **II.2 CONFIGURATION**

Une sérigraphie sur un film plastique attachée à la carte reprend la configuration de chacun des cavaliers. Les configurations à la livraison sont grisées dans les tableaux suivants.

# **Cavalier JP1**

| JP1        |                              |

|------------|------------------------------|

| 1-2 fermé  | Simulation batterie active   |

| 1-2 ouvert | Simulation batterie inactive |

| JP1        |                      |

|------------|----------------------|

| 3-4 fermé  | Batterie Connectée   |

| 3-4 ouvert | Batterie déconnectée |

Attention, la configuration JP1 : 1-2 fermé et 3-4 fermé est interdite.

# **Cavalier JP2**

| JP2       |           | Mode              |  |

|-----------|-----------|-------------------|--|

| 2-3 fermé | 5-6 fermé | Firmware          |  |

| 1-2 fermé | 5-6 fermé | Stand Alone       |  |

| 2-3 fermé | 4-5 fermé | Réservé<br>ACKSYS |  |

| 1-2 fermé | 4-5 fermé | MCXDOS            |  |

# **Cavalier JP3**

| JP3                       |                    |

|---------------------------|--------------------|

| 1-2 fermé Watchdog activé |                    |

| 2-3 fermé                 | Watchdog désactivé |

| JP3       | Action RESET PCI |

|-----------|------------------|

| 4-5 fermé | RESET MCX-PCI    |

| 5-6 fermé | Aucune           |

# II.3 DEMARRAGE DE LA CARTE

A la mise sous tension, la carte MCXCPCI effectue un autotest avec affichage sur le groupe de 8 leds du test en cours d'exécution.

En cas d'erreur, les leds conservent leur état et permettent d'identifier immédiatement la cause de l'erreur.

La signification des différents codes est la suivante :

| LED | 0         | 1         | 2         | 3          | 4          | 5         | 6         | 7 |

|-----|-----------|-----------|-----------|------------|------------|-----------|-----------|---|

|     | $\bigcap$ |           | $\bigcap$ | $\bigcirc$ |            | $\bigcap$ | $\bigcap$ |   |

|     | $\bigcup$ | $\bigcup$ | $\bigcup$ | $\bigcup$  | $\bigcirc$ | $\bigcup$ | $\bigcup$ |   |

| Bit | 0         | 1         | 2         | 3          | 4          | 5         | 6         | 7 |

| Code 01h | 6                                                     |

|----------|-------------------------------------------------------|

| Code 02h | C                                                     |

| Code 03h |                                                       |

| Code 04h |                                                       |

| Code 05h | Erreur sur les TIMERS système.                        |

| Code 06h | Erreur dans le test d'adresse de 1 <sup>er</sup> 64 K |

|          | ou bien mauvaise configuration. mémoire.              |

| Code 07h | Erreur dans le test de 1 <sup>er</sup> 64 K ram.      |

| Code 08h | Erreur sur contrôleur d'INT.                          |

| Code 09h | Détection d'INT non attendue.                         |

| Code 0Ah | Pas d'interruption TIMER.                             |

| Code 0Bh | CPU déjà en mode protégé.                             |

| Code 0Ch |                                                       |

| Code 0Dh | Pas de refresh de la mémoire.                         |

| Code 0Eh | Erreur sur le contrôleur du clavier.                  |

| Code 0Fh | Impossible d'entrer en mode protégé.                  |

| Code 10h |                                                       |

| Code 11h | Erreur sur registre LDT.                              |

| Code 12h | Erreur dans le registre de tâche.                     |

| Code 13h | Erreur sur instruction LSL.                           |

| Code 14h | Erreur sur instruction LAR.                           |

| Code 15h | Erreur sur VERR / VERW.                               |

| Code 16h | Erreur sur ligne d'adresse A20.                       |

| Code 17h | Exception non attendue.                               |

| Code 18h | Shutdown pendant le test mémoire.                     |

| Code 19h | Erreur checksum Copyright.                            |

| Code 1Ah | Erreur checksum paramètres.                           |

| Code C0h | Erreur dans le test mémoire.                          |

| Code C1h | Erreur sur signal IO/CHECK.                           |

| Code C2h | « Watchdog time out ».                                |

| Code C4h | « Bus time out ».                                     |

|          |                                                       |

Les codes erreurs suivants ne sont significatifs qu'en mode «Built-In Firmware» :

| Code 81h | Erreur sur UART, SCC ou SCA.               |

|----------|--------------------------------------------|

| Code 82h | Erreur mémoire double accès.               |

| Code 83h | Erreur TRAP non attendue.                  |

| Code 84h | Erreur mémoire tampon.                     |

| Code 85h | Erreur checksum firmware.                  |

| Code 86h | Erreur batterie Lithium.                   |

| Code 87h | Erreur interruption MCXCPCI vers PC.       |

| Code 88h | Erreur « watchdog ».                       |

| Code 89h | Erreur accès FIFO, flags ou Int, côté      |

|          | MCXCPCI ou erreur lecture Fifo par         |

|          | MCXCPCI.                                   |

| Code 8Bh | Erreur SCC pendant test DMA haute vitesse. |

| Code 8Ch | Faute de protection générale.              |

| Code 8Dh | Erreur taille mémoire.                     |

| Code 8Eh | Interruption NMI reçue.                    |

|          |                                            |

En mode Built-In Firmware, lorsque l'auto-test a été effectué correctement, les leds 0 à 7 s'allument et s'éteignent successivement indiquant que la carte attend maintenant son code de départ

- "RUN 01" : lancement du logiciel de base

- "RUN 02" : lancement du logiciel multiprotocole

En mode MCXDOS, lorsque l'auto-test a été effectué correctement, les leds 0 à 7 s'éteignent indiquant que la carte attend maintenant son code de départ

- "RUN 99": boot en mode MCXDOS.

- "RUN 96": boot sur le disque Compact Flash.

En mode Stand-Alone, lorsque l'auto-test a été effectué correctement, les leds 0 à 7 s'éteignent, et la carte démarre automatiquement sur le disque Compact Flash.

Si l'une des erreurs, citées ci-dessus, est rencontrée à la mise sous tension de la carte, il est conseillé de vous adresser à votre revendeur qui prendra toutes les dispositions utiles afin de réparer le matériel dans le meilleur délai.

#### II.4 HOT SWAP

La carte MCXCPCI répond aux spécifications CompactPCI Hot Swap specification PICMG 2.1. Elle est compatible avec les plateformes de type « Hight availability », « Full » et « Basic » Hot swap.

La carte MCXCPCI est dotée d'un contrôleur hot swap qui sécurise l'insertion et l'extraction « à chaud » de la carte dans des systèmes CompactPCI compatibles « hot plug ».

La MCXCPCI intègre des circuits de coupure qui protègent les alimentations +12V, +5V, +3.3V, et -12V en surintensité (court-circuit). Elle peut être insérée dans un système actif, ou retirée, sans jamais provoquer la détérioration du P.C hôte ou de la carte elle même

L'espace de configuration PCI de la carte MCXCPCI intègre le « Hot Swap Register Block (HS\_CSR) » ce qui permet au P.C. hôte, si il possède un service de gestion Hot Swap :

- d'autoriser les extractions, en commandant la LED bleu en façade de la carte (Led allumée => extraction autorisée).

- de configurer et d'attribuer les ressources PCI à la carte suite à l'insertion, afin de la rendre fonctionnelle.

# **Séquence d'insertion:**

- Dévérouiller les fixations en façade (vers l'extérieur)

- Insérer la carte dans un slot

- Verouiller les fixations en prise sur le chassis.

- La carte doit démarrer la séquence d'autotest.

Si la LED bleu reste allumée, c'est qu'un problème à été détecté sur la carte et gène sa mise en route.

## Séquence d'extraction :

- Déverouiller légèrement les fixations sans sortir la carte du slot

- Attendre que la LED bleu s'allume

- Retirer la carte

# III. LES EXTENSIONS PCB570-2, PCB570-4, PCB570-4P, PCB570-2R, PCB570-4R

Associée à l'extension PCB570-2, la carte MCXCPCI/0 devient la carte MCXCPCI/570-2. Associée à l'extension PCB570-4 et à un boîtier de connexion 570-BP, la carte MCXCPCI/0 devient la carte MCXCPCI/570-4.

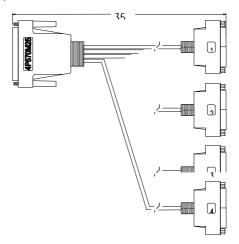

Associée à l'extension PCB570-4P et à un câble pieuvre 4P570M25, la carte MCXCPCI/0 devient la carte WAN-HDLC/4C.

Associée à l'extension PCB570-2R et à une carte REAR I/O CPCIRIO2, la carte MCXCPCI/0 devient la carte MCXCPCI/570-2R.

Associée à l'extension PCB570-4R et à une carte REAR I/O CPCIRIO2, la carte MCXCPCI/0 devient la carte MCXCPCI/570-4R.

Les cartes MCXCPCI/570-2(-R), MCXCPCI/570-4(-R) et WAN-HDLC/4C offrent respectivement 2, 4 et 4 ports série hauts débits en mode asynchrone, synchrone orienté bit (type HDLC) et synchrone orienté caractère (type MONOSYNC ou BISYNC) avec interface électrique multiprotocole programmable :

- RS232/V24/V28 (débit binaire assuré à 256 Kbits/s)

- RS422/V11 (débit binaire limité à 5Mbits/s en mode synchrone)

- RS485 (débit binaire limité à 5Mbits/s en mode synchrone)

- RS449 (débit binaire limité à 5Mbits/s en mode synchrone)

- V35 (débit binaire limité à 1Mbits/s en mode synchrone)

- V36 (débit binaire limité à 5Mbits/s en mode synchrone)

- EIA530 (1987) (débit binaire limité à 5Mbits/s en mode synchrone)

- EIA530-A (1992) (débit binaire limité à 5Mbits/s en mode synchrone)

La structure matérielle de ces cartes (contrôleurs DMA intégrés, bus de données 16 bits, FIFO Tx/Rx 32 octets, DMA mode chaîné en HDLC, ...) les destinent tout particulièrement à la gestion de protocoles de communication complexes, en effet les opérations d'émission et de réception de caractères peuvent être prises en compte par les contrôleurs DMA intégrés, laissant ainsi le CPU de la carte MCXCPCI/0 disponible pour la gestion du protocole liaison de données.

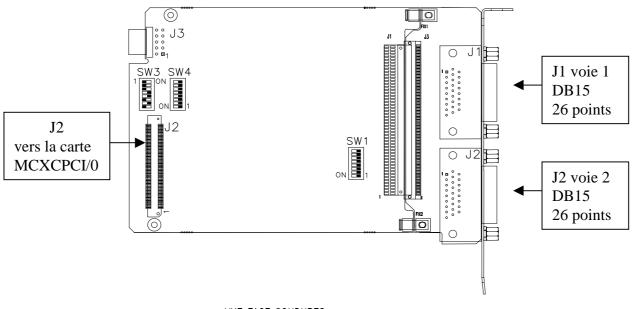

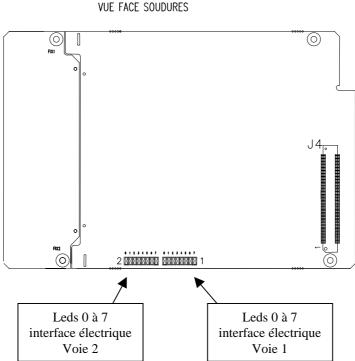

# III.1 SYNOPTIQUE DE L'EXTENSION PCB570-2

# VUE FACE COMPOSANTS

VUE FACE SOUDURES

Connecteur J1 : Connecteur haute densité DB 26 points femelle voie 1

Connecteur J2 : Connecteur haute densité DB 26 points femelle voie 2

Connecteur J2 : Connecteur vers la carte MCXCPCI/0 (Bus 16 bits)

Connecteur J3: Connecteur 10 broches fournissant les synchros des voies 1, 2.

Connecteur J4: Connecteur optionnel pour brancher une deuxième extension PCB-

Switch SW1: Commutateur pour synchro DSR et la terminaison des voies 1 et 2.

Switch SW3, SW4: Commutateurs 8 points pour attribuer les DMA et IRQ.

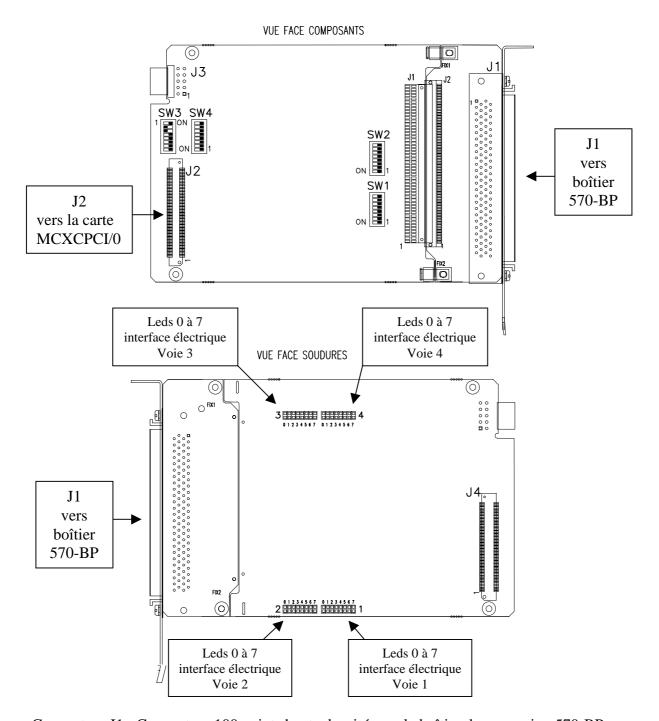

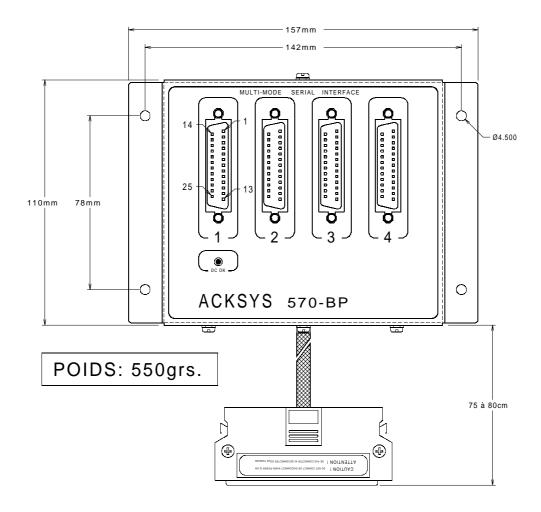

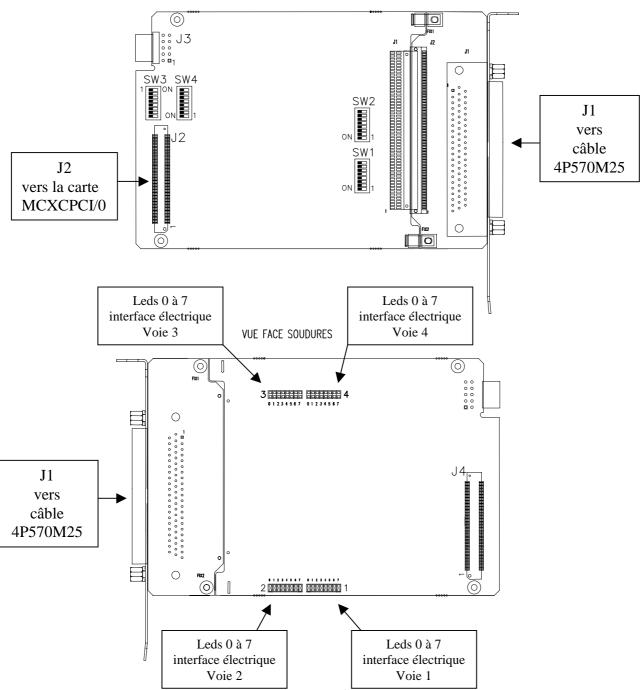

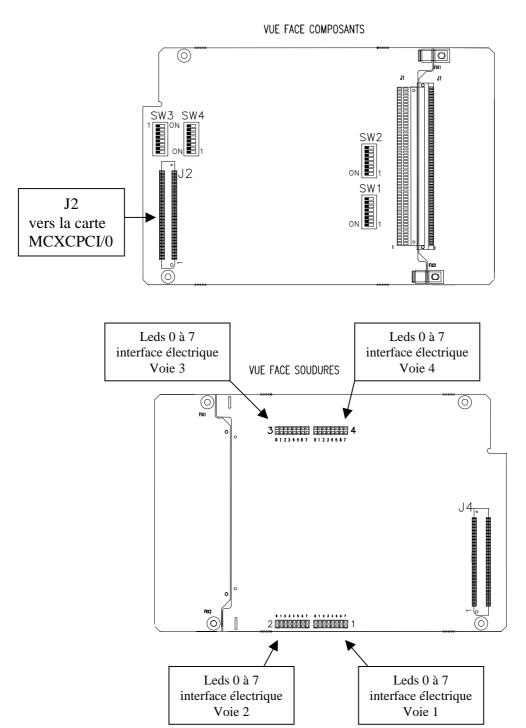

# III.2 SYNOPTIQUE DE L'EXTENSIONS PCB570-4

L'extension PCB570-4 est constituée d'une carte PCB570-4, et d'un boîtiers 570-BP. Dans cette configuration, la carte occupe 1 slot CPCI dans le P.C.

Connecteur J1 : Connecteur 100 points haute densité vers le boîtier de connexion 570-BP.

Connecteur J2: Connecteur vers la carte MCXCPCI/0 (Bus 16 bits).

Connecteur J3: Connecteur 10 broches fournissant les synchros des voies 1, 2, 3, 4.

Connecteur J4: Connecteur optionnel pour brancher une deuxième extension PCB-.

Switch SW1: Commutateur pour synchro DSR et la terminaison des voies 1 et 2.

Switch SW2: Commutateur pour synchro DSR et la terminaison des voies 3 et 4.

Switch SW3, SW4: Commutateurs pour attribuer les DMA et IRQ.

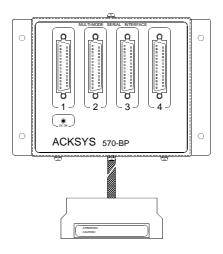

# III.2.1 Le boîtier de connexion 570-BP

Il est impératif de connecter le boîtier 570-BP à la carte MCXCPCI/570-4, P.C. hors tension.

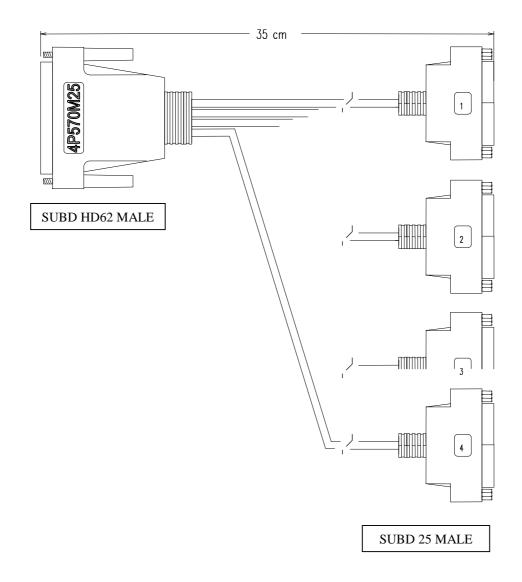

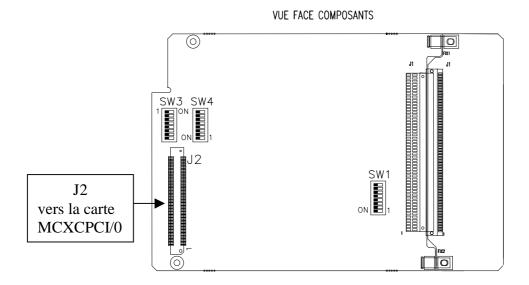

# III.3 SYNOPTIQUE DE L'EXTENSION PCB570-4P

L'extension PCB570-4P est constituée d'une carte PCB570-4P, et d'un câble de répartition 4 voies. Dans cette configuration, la carte occupe 1 slot CPCI dans le P.C.

VUE FACE COMPOSANTS

Connecteur J1: Connecteur 100 points haute densité vers câble 4P570M25.

Connecteur J2: Connecteur vers la carte MCXCPCI/0 (Bus 16 bits).

Connecteur J3: Connecteur 10 broches fournissant les synchros des voies 1, 2, 3, 4.

Connecteur J4: Connecteur optionnel pour brancher une deuxième extension PCB-.

Switch SW1: Commutateur pour synchro DSR et la terminaison des voies 1 et 2.

Switch SW2: Commutateur pour synchro DSR et la terminaison des voies 3 et 4.

Switch SW3, SW4: Commutateurs pour attribuer les DMA et IRQ.

# III.3.1 Le câble de répartition 4P570M25

Il est impératif de connecter le câble 4P570M25 à la carte WAN-HDLC/4C, P.C. hors tension.

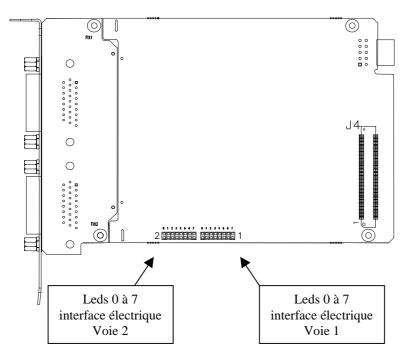

# III.4 SYNOPTIQUE DE L'EXTENSION PCB570-2R

L'extension PCB570-2R est constituée d'une carte PCB570-2R, et d'une carte REAR I/O 2 voies. Dans cette configuration, la carte occupe 1 slot CPCI dans le P.C.

Connecteur J2: Connecteur vers la carte MCXCPCI/0 (Bus 16 bits).

Connecteur J4: Connecteur optionnel pour brancher une deuxième extension PCB-.

Switch SW1: Commutateur pour synchro DSR et la terminaison des voies 1 et 2.

Switch SW2: Commutateur pour synchro DSR et la terminaison des voies 3 et 4.

Switch SW3, SW4: Commutateurs pour attribuer les DMA et IRQ.

# III.5 SYNOPTIQUE DE L'EXTENSION PCB570-4R

L'extension PCB570-4R est constituée d'une carte PCB570-4R, et d'une carte REAR I/O 4 voies. Dans cette configuration, la carte occupe 1 slot CPCI dans le P.C.

Connecteur J2: Connecteur vers la carte MCXCPCI/0 (Bus 16 bits).

Connecteur J4: Connecteur optionnel pour brancher une deuxième extension PCB-.

Switch SW1: Commutateur pour synchro DSR et la terminaison des voies 1 et 2.

Switch SW2: Commutateur pour synchro DSR et la terminaison des voies 3 et 4.

Switch SW3, SW4: Commutateurs pour attribuer les DMA et IRQ.

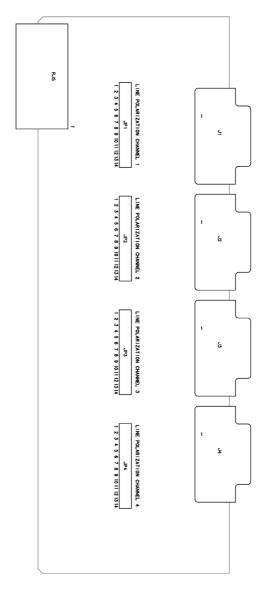

## III.5.1 La carte REAR I/O CPCIRIO2

La carte REAR I/O est composée de 4 connecteurs 26 points J1 à J4 haute densité femelle, et d'un groupe de cavalier à utiliser pour fournir la polarisation de ligne en RS485 si elle est requise. Sur la version 2 voies, les connecteurs J3 et J4 sont câblés mais non utilisables.

JPx-1 & JPx-2 : Polarisation de ligne signal RxD voie x.

JPx-3 & JPx-4 : Polarisation de ligne signal TxClkIn voie x

JPx-5 & JPx-6 : Polarisation de ligne signal RxClkIn voie x

JPx-7 & JPx-8 : Polarisation de ligne signal CTS voie  $\boldsymbol{x}$

JPx-9 & JPx-10 : Polarisation de ligne signal DCD voie x

JPx-11 & JPx-12 : Polarisation de ligne signal DSR voie x

JPx-13 & JPx-14 : Polarisation de ligne signal RI voie x

x représente le numéro de la voie (JP1-3 & JP1-4 pour les cavaliers N° 3 & 4 de la voie 1).

# III.6 CONFIGURATION CARTES PCB570-X

# Les commutateurs SW1, SW2, SW3, SW4

| SW1-1                                             | ON | Activation signal de synchronisation DSR          |        |

|---------------------------------------------------|----|---------------------------------------------------|--------|

| SW1-2                                             | ON | Résistance $120\Omega$ de terminaison sur RxD     | Voie 1 |

| SW1-3                                             | ON | Résistance $120\Omega$ de terminaison sur TxClkIn | voie i |

| SW1-4                                             | ON | Résistance $120\Omega$ de terminaison sur RxClk   |        |

| SW1-5                                             | ON | Activation signal de synchronisation DSR          |        |

| SW1-6                                             | ON | Résistance $120\Omega$ de terminaison sur RxD     | Voie 2 |

| SW1-7                                             | ON | Résistance $120\Omega$ de terminaison sur TxClkIn | voie 2 |

| SW1-8 ON Résistance 120Ω de terminaison sur RxClk |    |                                                   |        |

| SW2-1 | ON | Activation signal de synchronisation DSR          |        |  |

|-------|----|---------------------------------------------------|--------|--|

| SW2-2 | ON | Résistance $120\Omega$ de terminaison sur RxD     | W : 2  |  |

| SW2-3 | ON | Résistance $120\Omega$ de terminaison sur TxClkIn | Voie 3 |  |

| SW2-4 | ON | Résistance 120Ω de terminaison sur RxClk          |        |  |

| SW2-5 | ON | Activation signal de synchronisation DSR          |        |  |

| SW2-6 | ON | Résistance $120\Omega$ de terminaison sur RxD     | Vais 4 |  |

| SW2-7 | ON | Résistance $120\Omega$ de terminaison sur TxClkIn | Voie 4 |  |

| SW2-8 | ON | Résistance 120Ω de terminaison sur RxClk          |        |  |

# CONFIGURATION A LA LIVRAISON POUR UNE CARTE PCB570-X OU WAN-HDLC/4C RESISTANCES DE TERMINAISON CONNECTEES LE SIGNAL DE SYNCHRONISATION DSR N'EST PAS ACTIF SW1 -2...8 ON SW2-2...8 ON

SW1-1 OFF SW2-1 OFF

#### SW3 et SW4 attribuent :

- Le numéro de la première voie.

- Un canal DMA et un niveau d'interruption à chaque contrôleur de communication SCA.

# Attention SW3 et SW4 sont configurés en usine et réservés à l'usage d'ACKSYS.

# Attribution du numéro de la première voie de la carte

| N° première voie | SW4-8 |

|------------------|-------|

| 1                | OFF   |

| 5                | ON    |

#### Attribution canal DMA aux SCA 1 ou SCA 3

| Canal DMA | SW3-2 | SW3-3 | SW3-4 | SW3-5 |

|-----------|-------|-------|-------|-------|

| 1         | OFF   | OFF   | ON    | ON    |

| 3         | ON    | ON    | OFF   | OFF   |

# Attribution niveau IRQ aux SCA 1 ou SCA 3

| IRQ | SW3-7 | SW4-2 |

|-----|-------|-------|

| 3   | ON    | OFF   |

| 15  | OFF   | ON    |

#### Attribution niveau IRO aux SCA 2 ou SCA 4

| IRQ | SW3-6 | SW4-1 |

|-----|-------|-------|

| 4   | ON    | OFF   |

| 12  | OFF   | ON    |

#### Attribution canal DMA aux SCA 2 ou SCA 4

| Canal DMA | SW3-1 | SW3-8 | SW4-3 | SW4-4 |

|-----------|-------|-------|-------|-------|

| 2         | ON    | ON    | OFF   | OFF   |

| 5         | OFF   | OFF   | ON    | ON    |

#### Non utilisés

SW4-5 SW4-6 SW4-7

## CONFIGURATION A LA LIVRAISON POUR UNE CARTE PCB570-2 (-R)

Le numéro 1 est attribué à la 1<sup>ère</sup> voie

Le canal DMA 1, l'interruption IRQ3 sont attribués au SCA 1

## CONFIGURATION A LA LIVRAISON POUR UNE CARTE PCB570-4 (-R)

Le numéro 1 est attribué à la 1<sup>ère</sup> voie

Le canal DMA 1, l'interruption IRQ3 sont attribués au SCA 1

Le canal DMA 2, l'interruption IRQ4 sont attribués au SCA 2

# CONFIGURATION A LA LIVRAISON POUR UNE CARTE WAN-HDLC/4C

Le numéro 1 est attribué à la 1<sup>ère</sup> voie

Le canal DMA 1, l'interruption IRQ3 sont attribués au SCA 1

Le canal DMA 2, l'interruption IRQ4 sont attribués au SCA 2

# III.7 ATTRIBUTION DES SIGNAUX SUR LES CONNECTEURS

# • Les interfaces électriques

| Mnémonique  | RS232 | V35   | RS422 | RS485 | RS449/<br>EIA530 | EIA-530A | V36   |

|-------------|-------|-------|-------|-------|------------------|----------|-------|

| TxD(A)      | V28   | V35   | V11   | RS485 | V11              | V11      | V11   |

| TxD(B)      | HiZ   | V35   | V11   | RS485 | V11              | V11      | V11   |

| DTR(A)*     | V28   | V28   | V11   | RS485 | V11              | V10      | V10   |

| DTR(B)*     | HiZ   | HiZ   | V11   | RS485 | V11              | HiZ      | HiZ   |

| RTS(A)      | V28   | V28   | V11   | RS485 | V11              | V11      | V10   |

| RTS(B)      | HiZ   | HiZ   | V11   | RS485 | V11              | V11      | HiZ   |

| TxClkOut(A) | V28   | V35   | V11   | RS485 | V11              | V11      | V11   |

| TxClkOut(B) | HiZ   | V35   | V11   | RS485 | V11              | V11      | V11   |

| RxD(A)      | V28   | V35   | V11   | RS485 | V11              | V11      | V11   |

| RxD(B)      | >12KΩ | V35   | V11   | RS485 | V11              | V11      | V11   |

| RxClkIn(A)  | V28   | V35   | V11   | RS485 | V11              | V11      | V11   |

| RxClkIn(B)  | >12KΩ | V35   | V11   | RS485 | V11              | V11      | V11   |

| CTS(A)      | V28   | V28   | V11   | RS485 | V11              | V11      | V10   |

| CTS(B)      | >12KΩ | >12KΩ | V11   | RS485 | V11              | V11      | >12KΩ |

| DSR(A)*     | V28   | V28   | V11   | RS485 | V11              | V10      | V10   |

| DSR(B)*     | >12KΩ | >12KΩ | V11   | RS485 | V11              | >12KΩ    | >12KΩ |

| DCD(A)*     | V28   | V28   | V11   | RS485 | V11              | V11      | V10   |

| DCD(B)*     | >12KΩ | >12KΩ | V11   | RS485 | V11              | V11      | >12KΩ |

| RI(A)*      | V28   | V28   | V11   | RS485 | V10              | V10      | V10   |

| RI(B)*      | >12KΩ | >12KΩ | V11   | RS485 | >12KΩ            | >12KΩ    | >12KΩ |

| TxClkIn(A)  | V28   | V35   | V11   | RS485 | V11              | V11      | V11   |

| TxClkIn(B)  | >12KΩ | V35   | V11   | RS485 | V11              | V11      | V11   |

HiZ: Haute impédance

# Note pour les cartes MCXCPCI/570-x uniquement :

Il est impératif de polariser tous les signaux différentiels entrants (CTS, DCD, DSR et RI) afin de garantir un état stable en sortie (au niveau TTL). Si certains de ces signaux ne sont pas utilisés par votre application, vous pouvez soit :

Les reboucler les avec les signaux différentiels sortant RTS ou DTR.

Exemple de rebouclage de RTS du DCD

RTS (A) sur DCD (A)

RTS (B) sur DCD(B)

Polariser le signal B uniquement via l'alimentation disponible sur la broche 25.

Exemple de polarisation de DCD

DCD (A) non connecté

DCD (B) relié à la broche 25

Sur les versions REAR I/O connecter les cavaliers correspondants aux signaux à polariser/ Exemple de polarisation de DCD sur la voie 1

Cavalier de JP1-9 et cavalier de JP1-10 raccordés.

$<sup>&</sup>gt;12K\Omega$ : par rapport à la masse

<sup>\*</sup> signaux non connectés sur la carte WAN-HDLC/4C

## • Les résistances de terminaison et de polarisation :

Certaines configurations d'interface électrique nécessitent des résistances de terminaison (voir recommandation V11 du CCITT) et de polarisation de lignes (RS485, RS422 avec plusieurs transmetteurs).

Notez que seules les résistances de terminaison peuvent être connectées en interne sur la carte grâce aux commutateurs SW1 et SW2.

Les résistances de polarisation quand à elle devront être intégrées dans le câble de raccordement sur les cartes MCXCPCI/570-2, MCXCPCI/570-4, WAN-HDLC/4C.

Pour connecter les résistances de polarisation sur les cartes MCXCPCI/570-2-R et MCXCPCI/570-4-R, il suffit simplement de connecter les cavaliers sur les broches correspondantes de JP1 à JP4.

Pour la polarisation d'une paire (A,B),

connecter une résistance de  $470\Omega$  à  $1K\Omega$  (1/4W 5%) entre le signal A et la masse signal (GND broche 7 ou 26) et entre le signal B et l'alimentation +5V (broche 25) ou

Connecter les cavaliers correspondants sur JP1 à JP4.

## III.7.1 Extension PCB570-2

Les signaux associés aux voies série 1 et 2 sont respectivement disponibles sur les connecteurs 26 points J1 et J2 du circuit imprimé PCB570-2.

BROCHAGE DES 2 CONNECTEURS 26 POINTS J1 ET J2 HAUTE DENSITE FEMELLE (FORMAT DB15 TAILLE A)

| N° Broche | Signal                                                 | Mnémonique          | Direction  |  |

|-----------|--------------------------------------------------------|---------------------|------------|--|

| 1         | P.G                                                    | Protective Ground   |            |  |

| 2         | TxD                                                    | Transmit Data       | Output (A) |  |

| 14        | TxD                                                    | Transmit Data       | Output (B) |  |

| 3         | RxD                                                    | Receive Data        | Input (A)  |  |

| 16        | RxD                                                    | Receive Data        | Input (B)  |  |

| 24        | TxClkOut                                               | Transmit Clock      | Output (A) |  |

| 11        | TxClkOut                                               | Transmit Clock      | Output (B) |  |

| 15        | TxClkIn                                                | Transmit Clock      | Input (A)  |  |

| 12        | TxClkIn                                                | Transmit Clock      | Input (B)  |  |

| 17        | RxClkIn                                                | Receive Clock       | Input (A)  |  |

| 9         | RxClkIn                                                | Receive Clock       | Input (B)  |  |

| 20        | DTR                                                    | Data Terminal Ready | Output (A) |  |

| 23        | DTR                                                    | Data Terminal Ready | Output (B) |  |

| 4         | RTS                                                    | Request To Send     | Output (A) |  |

| 19        | RTS                                                    | Request To Send     | Output (B) |  |

| 5         | CTS                                                    | Clear To Send       | Input (A)  |  |

| 13        | CTS                                                    | Clear To Send       | Input (B)  |  |

| 8         | DCD                                                    | Data Carrier Detect | Input (A)  |  |

| 10        | DCD                                                    | Data Carrier Detect | Input (B)  |  |

| 6         | DSR                                                    | Data Set Ready      | Input (A)  |  |

| 18        | DSR                                                    | Data Set Ready      | Input (B)  |  |

| 22        | RI                                                     | Ring Indicator      | Input (A)  |  |

| 21        | RI                                                     | Ring Indicator      | Input (B)  |  |

| 7, 26     | GND                                                    |                     |            |  |

| 25        | +5V (utile en mode RS485 pour fournir la polarisation) |                     |            |  |

La sortie +5V (broche 25) de chaque connecteur (J1 et J2) est protégée par un fusible thermique réarmable. En cas de court-circuit accidentel sur les connecteurs J1 et J2, il est recommandé d'arrêter le système et de détecter la cause du court-circuit. Attention la tension ne peut être rétablie qu'après un délai de 20 secondes.

**Le connecteur J3** fournit les signaux de synchronisation /SYNC de chacune des voies de la carte. Le signal de synchronisation est généré par la broche /SYNC du SCA (voir SCA user's manual).

| J3-1             | GND                              |  |

|------------------|----------------------------------|--|

| J3-2             | Signal de synchronisation voie 1 |  |

| J3-3             | GND                              |  |

| J3-4             | Signal de synchronisation voie 2 |  |

| J3-5             | GND                              |  |

| J3-6             | Non utilisé                      |  |

| J3-7 GND         |                                  |  |

| J3-8 Non utilisé |                                  |  |

| J3-9             | GND                              |  |

| J3-10            | GND                              |  |

# III.7.2 Extensions PCB570-4

Les signaux associés aux voies série 1, 2, 3 et 4 sont respectivement disponibles sur les connecteurs numérotés 1, 2, 3 et 4 du boîtier 570-BP.

BROCHAGE DES 4 CONNECTEURS 25 POINTS MALE (FORMAT DB25 TAILLE C)

DU BOITIER 570-BP

| N° Broche | Signal                                                 | Mnémonique          | Direction  |  |

|-----------|--------------------------------------------------------|---------------------|------------|--|

| 1         | P.G                                                    | Protective Ground   |            |  |

| 2         | TxD                                                    | Transmit Data       | Output (A) |  |

| 14        | TxD                                                    | Transmit Data       | Output (B) |  |

| 3         | RxD                                                    | Receive Data        | Input (A)  |  |

| 16        | RxD                                                    | Receive Data        | Input (B)  |  |

| 24        | TxClkOut                                               | Transmit Clock      | Output (A) |  |

| 11        | TxClkOut                                               | Transmit Clock      | Output (B) |  |

| 15        | TxClkIn                                                | Transmit Clock      | Input (A)  |  |

| 12        | TxClkIn                                                | Transmit Clock      | Input (B)  |  |

| 17        | RxClkIn                                                | Receive Clock       | Input (A)  |  |

| 9         | RxClkIn                                                | Receive Clock       | Input (B)  |  |

| 20        | DTR                                                    | Data Terminal Ready | Output (A) |  |

| 23        | DTR                                                    | Data Terminal Ready | Output (B) |  |

| 4         | RTS                                                    | Request To Send     | Output (A) |  |

| 19        | RTS                                                    | Request To Send     | Output (B) |  |

| 5         | CTS                                                    | Clear To Send       | Input (A)  |  |

| 13        | CTS                                                    | Clear To Send       | Input (B)  |  |

| 8         | DCD                                                    | Data Carrier Detect | Input (A)  |  |

| 10        | DCD                                                    | Data Carrier Detect | Input (B)  |  |

| 6         | DSR                                                    | Data Set Ready      | Input (A)  |  |

| 18        | DSR                                                    | Data Set Ready      | Input (B)  |  |

| 22        | RI                                                     | Ring Indicator      | Input (A)  |  |

| 21        | RI                                                     | Ring Indicator      | Input (B)  |  |

| 7         | GND                                                    |                     |            |  |

| 25        | +5V (utile en mode RS485 pour fournir la polarisation) |                     |            |  |

Un voyant lumineux indique, lorsqu'il est allumé, que le dispositif de connexion 570-BP est correctement alimenté par le système.

Ce voyant peut s'éteindre pour les raisons suivantes :

Court-circuit sur un connecteur Sub-D 25 points Surcharge des alimentations sur les Sub-D 25 points

En cas de court-circuit accidentel sur un des connecteurs, il est recommandé d'arrêter le système et de détecter la cause du court-circuit. Attention la tension ne peut être rétablie qu'après un délai de 20 secondes à cause d'un fusible thermique de protection réarmable.

# NOTE IMPORTANTE concernant l'incompatibilité entre le brochage EIA530 et EIA530-A défini par la norme et celui retenu pour l'extension PCB570-4.

|           | Brochage compatible<br>Norme EIA530-A | Brochage EIA530-A carte PCB570-4 |

|-----------|---------------------------------------|----------------------------------|

| Broche 18 | LL (Local Loopback)                   | DSR (B)                          |

| Broche 21 | RL (Remote Loopback)                  | >12 KΩ / GND                     |

| Broche 25 | TM (Test Mode)                        | +5V                              |

|           | Brochage compatible  | Brochage EIA530  |

|-----------|----------------------|------------------|

|           | Norme EIA530         | carte PCB570-4   |

| Broche 22 | DSR (B)              | Non utilisé (RI) |

| Broche 18 | LL (Local Loopback)  | DSR (B)          |

| Broche 21 | RL (Remote Loopback) | >12 KΩ / GND     |

| Broche 25 | TM (Test Mode)       | +5V              |

#### Note:

La norme RS232 imposant que le signal Ring Indicator soit affecté à la broche 22, les broches 18 et 22 de la carte MCXCPCI/570-4 ne sont pas compatibles avec la norme EIA530.

Sur l'extension PCB570-4, le **connecteur J3** fournit les signaux de synchronisation /SYNC de chacune des voies de la carte. Le signal de synchronisation est généré par la broche /SYNC du SCA (voir SCA user's manual).

| J3-1  | GND                              |  |  |

|-------|----------------------------------|--|--|

| J3-2  | Signal de synchronisation voie 1 |  |  |

| J3-3  | GND                              |  |  |

| J3-4  | Signal de synchronisation voie 2 |  |  |

| J3-5  | GND                              |  |  |

| J3-6  | Signal de synchronisation voie 3 |  |  |

| J3-7  | GND                              |  |  |

| J3-8  | Signal de synchronisation voie 4 |  |  |

| J3-9  | GND                              |  |  |

| J3-10 | GND                              |  |  |

# III.7.3 Extensions PCB570-4P

Les signaux associés aux voies série 1, 2, 3 et 4 sont respectivement disponibles sur les connecteurs numérotés 1, 2, 3 et 4 du câble 4P570M25.

BROCHAGE DES 4 CONNECTEURS 25 POINTS MALE (FORMAT DB25 TAILLE C)

DU CABLE 4P570M25

| N° Broche | Signal             | Mnémonique                    | Direction  |

|-----------|--------------------|-------------------------------|------------|

| 1         | P.G                | Protective Ground             |            |

| 2         | TxD                | Transmit Data                 | Output (A) |

| 14        | TxD                | Transmit Data                 | Output (B) |

| 3         | RxD                | Receive Data                  | Input (A)  |

| 16        | RxD                | Receive Data                  | Input (B)  |

| 24        | TxClkOut           | Transmit Clock                | Output (A) |

| 11        | TxClkOut           | Transmit Clock                | Output (B) |

| 15        | TxClkIn            | Transmit Clock                | Input (A)  |

| 12        | TxClkIn            | Transmit Clock                | Input (B)  |

| 17        | RxClkIn            | Receive Clock                 | Input (A)  |

| 9         | RxClkIn            | Receive Clock                 | Input (B)  |

| 20        | N.C.               | Not Connected                 |            |

| 23        | N.C.               | Not Connected                 |            |

| 4         | RTS                | Request To Send               | Output (A) |

| 19        | RTS                | Request To Send               | Output (B) |

| 5         | CTS                | Clear To Send                 | Input (A)  |

| 13        | CTS                | Clear To Send                 | Input (B)  |

| 8         | N.C.               | Not Connected                 |            |

| 10        | N.C.               | Not Connected                 |            |

| 6         | N.C.               | Not Connected                 |            |

| 18        | N.C.               | Not Connected                 |            |

| 22        | N.C.               | Not Connected                 |            |

| 21        | N.C.               | Not Connected                 |            |

| 7         | GND                |                               |            |

| 25        | +5V (utile en mode | RS485 pour fournir la polaris | ation)     |

La sortie +5V (broche 25) de chaque connecteur est protégée par un fusible thermique réarmable. En cas de court-circuit accidentel sur les connecteurs de sortie, il est recommandé d'arrêter le système et de détecter la cause du court-circuit. Attention la tension ne peut être rétablie qu'après un délai de 20 secondes.

Le connecteur J3 fournit les signaux de synchronisation /SYNC de chacune des voies de la carte. Le signal de synchronisation est généré par la broche /SYNC du SCA (voir SCA user's manual).

| J3-1  | GND                              |

|-------|----------------------------------|

| J3-2  | Signal de synchronisation voie 1 |

| J3-3  | GND                              |

| J3-4  | Signal de synchronisation voie 2 |

| J3-5  | GND                              |

| J3-6  | Signal de synchronisation voie 3 |

| J3-7  | GND                              |

| J3-8  | Signal de synchronisation voie 4 |

| J3-9  | GND                              |

| J3-10 | GND                              |

# III.7.4 La carte REAR I/O pour extensions PCB570-2R et PCB470-4R

Les signaux associés aux voies série 1 à 4 sont respectivement disponibles sur les connecteurs 26 points J1 à J4 du circuit imprimé CPCIRIO2.

BROCHAGE DES 2 CONNECTEURS 26 POINTS J1 A J4 HAUTE DENSITE FEMELLE (FORMAT DB15 TAILLE A)

| N° Broche | Signal             | Mnémonique                    | Direction  |

|-----------|--------------------|-------------------------------|------------|

| 1         | P.G                | Protective Ground             |            |

| 2         | TxD                | Transmit Data                 | Output (A) |

| 14        | TxD                | Transmit Data                 | Output (B) |

| 3         | RxD                | Receive Data                  | Input (A)  |

| 16        | RxD                | Receive Data                  | Input (B)  |

| 24        | TxClkOut           | Transmit Clock                | Output (A) |

| 11        | TxClkOut           | Transmit Clock                | Output (B) |

| 15        | TxClkIn            | Transmit Clock                | Input (A)  |

| 12        | TxClkIn            | Transmit Clock                | Input (B)  |

| 17        | RxClkIn            | Receive Clock                 | Input (A)  |

| 9         | RxClkIn            | Receive Clock                 | Input (B)  |

| 20        | DTR                | Data Terminal Ready           | Output (A) |

| 23        | DTR                | Data Terminal Ready           | Output (B) |

| 4         | RTS                | Request To Send               | Output (A) |

| 19        | RTS                | Request To Send               | Output (B) |

| 5         | CTS                | Clear To Send                 | Input (A)  |

| 13        | CTS                | Clear To Send                 | Input (B)  |

| 8         | DCD                | Data Carrier Detect           | Input (A)  |

| 10        | DCD                | Data Carrier Detect           | Input (B)  |

| 6         | DSR                | Data Set Ready                | Input (A)  |

| 18        | DSR                | Data Set Ready                | Input (B)  |

| 22        | RI                 | Ring Indicator                | Input (A)  |

| 21        | RI                 | Ring Indicator                | Input (B)  |

| 7, 26     | GND                |                               | -          |

| 25        | +5V (utile en mode | RS485 pour fournir la polaris | ation)     |

La sortie +5V (broche 25) de chaque connecteur (J1 à J4) est protégée par un fusible thermique réarmable. En cas de court-circuit accidentel sur les connecteurs J1 à J4, il est recommandé d'arrêter le système et de détecter la cause du court-circuit. Attention la tension ne peut être rétablie qu'après un délai de 20 secondes.

# **ANNEXES**

| ANN  | EXE A POUR ECRIRE UN PILOTE DE PERIPHERIQUE        | A-1  |

|------|----------------------------------------------------|------|

| A.1  | Généralités                                        | A-1  |

| A.2  | ADRESSAGE DE LA MÉMOIRE DOUBLE ACCÈS               | A-2  |

| A.3  | ADRESSAGE DES REGISTRES D'ENTRÉES SORTIES          | A-3  |

| A.4  | INTERRUPTION CARTE VERS P.C.                       | A-5  |

| A.5  | INTERRUPTION P.C. VERS CARTE                       | A-5  |

| ANN  | EXE B POUR PROGRAMMER DANS LA CARTE                | B-1  |

| B.1  | ADRESSAGE DES REGISTRES D'ENTRÉES SORTIES GÉNÉRAUX | B-2  |

| B.2  | ADRESSAGE DES REGISTRES DE L'EXTENSION PCB570-X    | B-7  |

| B.2. | .1 Interruptions et canaux DMA                     | B-11 |

| ANN  | EXE C FICHE ERREUR                                 |      |

# ANNEXE A POUR ECRIRE UN PILOTE DE PERIPHERIQUE

Les informations fournies dans cette annexe donnent au programmeur tous les points d'entrées de la carte depuis le P.C, autrement dit tout le plan d'adressage de la carte depuis le P.C.

#### A.1 GENERALITES

Le dialogue entre la carte et le PC est assuré par les mécanismes suivants :

Une mémoire double accès de 32 Ko permettant l'échange bidirectionnel d'informations entre le P.C. et la carte.

Une interruption carte vers PC.

Une interruption PC vers carte.

Une FIFO de 512 octets accessible en écriture côté carte, et en lecture côté PC, constituant une alternative à la mémoire double accès pour l'échange d'informations unidirectionnel de la carte vers le PC.

Un ensemble de registres d'entrées-sorties qui permet diverses opérations :

Lecture de la FIFO

Lecture statuts de la FIFO (Vide, pleine, non vide ...)

Lecture position de commutateur de mode (JP2)

Désactivation de l'interruption envoyée par la carte

Reset de la carte

. . .

#### A.2 ADRESSAGE DE LA MEMOIRE DOUBLE ACCES

L'adresse de la mémoire double accès de 32 Ko est fixée par le BIOS PCI lors du démarrage de la machine, par exemple D00000h. Cette adresse est lisible dans le registre de configuration PCI appelé BAR1 (offset 14h).

Cette mémoire est en fait une page de l'espace mémoire de la carte, fixé par un numéro de page (voir illustration ci-dessous et paragraphe A.3).

| Adresse<br>fenêtre | N° PAGE |

|--------------------|---------|

| 0000:0000          | 00      |

| 0800:0000          | 01      |

| 1000:0000          | 02      |

| 1800:0000          | 03      |

| 2000:0000          | 04      |

| 2800:0000          | 05      |

| 3000:0000          | 06      |

| 3800:0000          | 07      |

| 4000:0000          | 08      |

| 4800:0000          | 09      |

| 5000:0000          | 0A      |

| 5800:0000          | 0B      |

| 6000:0000          | 0C      |

| 6800:0000          | 0D      |

| 7000 : 0000        | 0E      |

| 7800 : 0000        | 0F      |

| Adresse     | <b>N°PAGE</b> |

|-------------|---------------|

| Fenêtre     |               |

| 8000:0000   | 10            |

| 8800:0000   | 11            |

| 9000:0000   | 12            |

| 9800 : 0000 | 13            |

| A000:0000   | 14            |

| A800:0000   | 15            |

| B000:0000   | 16            |

| B800:0000   | 17            |

| C000:0000   | 18            |

| C800:0000   | 19            |

| D000:0000   | 1A            |

| D800:0000   | 1B            |

| E000:0000   | 1C            |

| E800:0000   | 1D            |

| F000:0000   | 1E            |

| F800:0000   | 1F            |

| •••         |               |

Le numéro de page est fixé par la carte après la phase d'autotest (Page 1Ah) et peut être modifié par le P.C (Voir paragraphe A.3) ou la carte elle même (Voir annexe B).

La mémoire double accès est adressée depuis le P.C comme de la mémoire standard sans aucune restriction, tous les modes d'accès étant supportés (8, 16 et 32 bits alignés ou pas).

#### A.3 ADRESSAGE DES REGISTRES D'ENTREES SORTIES

L'adresse de base d'entrées-sorties est fixée par le BIOS PCI lors du démarrage de la machine, par exemple C000h. Cette adresse est lisible dans le registre de configuration PCI appelé BAR0 (offset 10h).

# En lecture adresse Base + 0 - Registre de données de la FIFO

D0 à D7 ...... Ce registre permet de lire le contenu de la FIFO qui a précédemment été rempli par la carte (ce FIFO a une profondeur de 512 octets). Si la FIFO est vide, la valeur obtenue est 0FFH (255).

#### En écriture adresse Base + 0 – Reset carte

D0 à D7 ......L'écriture à cette adresse provoque un reset immédiat de la carte. L'état des bits D0 à D7 n'est pas significatif

#### En écriture/Lecture adresse Base + 1 - Ecriture/lecture N° de page

Les bits D0 à D7 permettent de sélectionner/lire une page logique de 32 Ko de la mémoire de la carte qui sera accessible dans la fenêtre du PC.

| D0 | Adresse page logique - A15. |

|----|-----------------------------|

| D1 | Adresse page logique - A16. |

| D2 | Adresse page logique - A17. |

| D3 | Adresse page logique - A18. |

| D4 | Adresse page logique - A19. |

| D5 | Adresse page logique – A20. |

| D6 | Adresse page logique – A21. |

| D7 | Adresse page logique – A22. |

Le bit d'adresse A23 est défini par écriture du bit D0 à l'adresse Base + 5. Attention, la première écriture dans ce registre désactive le choix de page fait par la carte lors de son initialisation.

#### En écriture adresse Base + 2 - Interruption PC VERS CARTE

#### En écriture adresse Base + 3 - DESACTIVATION IRQ CARTE VERS PC.

#### En lecture adresse Base + 3 - STATUS FIFO

D0 ...... Bit MCX-TO-PC-INT

Ce bit indique l'état du signal d'interruption généré par la carte vers le PC.

0: Interruption inactive.

1: Interruption active.

D1 ..... Bit FIFO-EMPTY

à 0, il indique que la FIFO est vide, à 1, il indique que la FIFO contient au moins un octet.

D2 ...... Bit MCX-INT

à 1, il indique que la carte n'a pas encore désactivé l'interruption générée par le PC.

D3 ...... Bit WIN-SET

à 0, ce bit indique que la carte a bien positionné sa page logique initiale et que les données lues dans la fenêtre du PC sont valides. A 1, il indique que cette opération n'a pas encore été réalisée ou bien que le PC a sélectionné une nouvelle page logique dans la fenêtre.

D4 ...... Bit JP2 1-2-3

à 1, il indique que le cavalier JP2 2-3 est fermé; dans le cas contraire, il indique que JP2 1-2 est fermé.

D5 ...... Bit JP2 4-5-6

à 1, il indique que le cavalier JP2 5-6 est fermé; dans le cas contraire, il indique que JP2 4-5 est fermé.

D6, D7 ...... Non significatifs

#### En lecture/Ecriture adresse Base +5 – Page logique bit A23

D0 ...... Ce bit représente le bit d'adresse A23 de la page logique de 32 Ko sélectionnée par le PC.

D1 à D7 ...... Non significatifs

# En lecture/Ecriture adresse Base +7 - Validation de l'interruption carte vers PC

D0 = 1 Interruption autorisée D0 = 0 Interruption interdite

D1 à D7 ...... Non significatifs

#### A.4 INTERRUPTION CARTE VERS P.C.

L'interruption utilisée par la carte dans le P.C. est fixée par le BIOS PCI lors du démarrage de la machine, par exemple IRQ12. Cette interruption est lisible dans le registre de configuration PCI appelé INTCFG (offset 3Ch).

Cette interruption est générée par la carte par écriture dans un registre situé dans le plan d'adressage d'entrées sorties de la carte. Cette interruption peut être désactivée par le P.C par une écriture dans le registre d'entrées sorties à l'adresse base +3.

# A.5 INTERRUPTION P.C. VERS CARTE

Le PC peut,

par écriture aux offsets 0 ou 1 de la mémoire double accès par écriture dans le port d'entrées sorties à l'adresse base+2,

générer une interruption sur la ligne IRQ9 de la carte.

#### ANNEXE BPOUR PROGRAMMER DANS LA CARTE

Ces informations sont destinées uniquement à l'écriture de programmes internes à la carte. Elles donnent donc au programmeur tout le plan d'adressage interne spécifique à la carte : Adressage leds, watchdog, timer100us, interruption, FIFO ... (paragraphe **B.1**)

Adressage carte mezzanine PCB-xxx (paragraphe **B.2**)

Toutes les informations relatives au bloc logique P.C sont dans le plan d'adressage standard du P.C et ne sont donc pas fournies dans cette annexe.

#### B.1 ADRESSAGE DES REGISTRES D'ENTREES SORTIES GENERAUX

Toutes les registres documentés dans ce paragraphe sont **dans le plan d'adressage d'entrées sortie** interne à la carte MCXCPCI/0. Attention, la plupart des registres n'ont pas la même signification en lecture et écriture.

# \* Ecriture adresse 80h - Affichage sur le groupe de 8 LEDS

| D0                                           | . Etat LED 0.                            |  |

|----------------------------------------------|------------------------------------------|--|

| D1                                           | . Etat LED 1.                            |  |

| D2                                           | . Etat LED 2.                            |  |

| D3                                           | . Etat LED 3.                            |  |

| D4                                           | . Etat LED 4.                            |  |

| D5                                           | . Etat LED 5.                            |  |

| D0                                           | . Etat LED 6.                            |  |

| D7                                           | . Etat LED 7 (LED de couleur différente) |  |

| Chaque bit à 1 correspond à une LED allumée. |                                          |  |

Chaque bit à 0 correspond à une LED éteinte.

# \* Ecriture adresse 500h - Activation de l'interruption vers le PC

| D0       | Ligne d'interruption   |

|----------|------------------------|

|          | 1 = active             |

|          | 0 = inactive           |

| D1 à D7. | Bits non significatifs |

# \* Ecriture/lecture adresse 501h – Programmation mémoire FLASH

| D0 Autorisation écritu        | re FLASH. Ce bit autorise la              |

|-------------------------------|-------------------------------------------|

| reprogrammation de            | la mémoire Flash contenant le BIOS        |

| et le firmware.               |                                           |

| 0 = Ecriture interdit         | te                                        |

| 1 = Ecriture autoris          | ée                                        |

| D1 Sélection FLASH            |                                           |

| 0 = Partie haute de           | 256 Ko                                    |

| 1 = Partie basse de           | 256 Ko                                    |

| Après avoir modifié           | é ce bit, il convient de réinitialiser la |

| carte.                        |                                           |

| D2 à D7 Bits non significatif | S                                         |

#### \* Ecriture adresse 503h - Reset IRQ9 provenant du PC.

D1 à D7 ..... Bits non significatifs

#### \* Ecriture adresse 504h - Registre de contrôle

D1 ..... Bit INT-MBX-ENABLE

Ce bit autorise les interruptions générées par le PC lors de l'écriture aux adresses 0 ou 1 de la mémoire double accès. Ces interruptions sont recueillies sur la ligne IRQ9 de la carte. Positionné à 0, ce bit interdit ce type d'interruption.

D2 ...... Ce bit contrôle le temps de déclenchement du watchdog. Le temps est de 1,6 secondes si D2 =1 et 100 ms si D2 =0

D3 ...... Adresse initiale de la fenêtre (A15).

D4 ...... Adresse initiale de la fenêtre (A16).

D5 ...... Adresse initiale de la fenêtre (A17).

D6 ...... Adresse initiale de la fenêtre (A18).

D7 ...... Adresse initiale de la fenêtre (A19).

Les bits D3 à D7 permettent de définir l'adresse de la page logique de 32 Ko initiale vue par le PC. Les autres bits d'adresse A20, A21, A22 et A23 sont forcés à 0 lors de cette opération. Il faut noter que cette page logique reste valide tant que le PC n'en a pas fixé une autre.

#### \* Lecture adresse 504h - Registre de status

D1 ...... Bit /Fifo Empty

Ce bit passe à 0 lorsque la FIFO est vide. Une lecture dans le registre de données de la FIFO à l'adresse 510h, quand ce bit est à 0, renvoie la valeur FFh.

D2 ...... Bit /Fifo Half Full

Ce bit passe à 0 lorsque la FIFO est à moitié pleine.

D3 ...... Indique l'état de la ligne d'interruption vers le PC.

0 = Interruption inactive

1 = Interruption active

D4 ...... Indique la position des cavaliers 1 2 3 de JP2

0 = 1-2 fermé

1 = 2-3 fermé

D5 ...... Indique la position des cavaliers 4 5 6 de JP2

0 = 4-5 fermé

1 = 5-6 fermé

D6 ...... Toujours à 1

D7 ...... Bit BAT-LOW

A 0, il indique que la batterie Lithium doit être remplacée, la lecture de ce bit n'est valide que si le bit BAT-TEST a été positionné à 0 (Adresse 504h, bit de poids 0).

#### \* Ecriture adresse 505h - Rafraîchissement du "Watchdog"

# \* Ecriture adresse 506h - Contrôle du "Watchdog"

> 0 = Wachdog inactif 1 = Watchdog actif

D1 à D7 ...... Bits non significatifs

#### \* Lecture adresse 507h - Lecture PAGE

En lecture, les bits D0 à D7 indiquent le numéro de page de 32 Ko sélectionné par le PC comme mémoire à double accès.

Le bit d'adresse A23 est défini par l'état du bit D0 du registre à l'adresse 513h.

#### \* Ecriture adresse 507h – Registre de données de la FIFO

D0 à D7 ...... Valeur sur 8 bits à écrire dans la FIFO

#### \* Ecriture adresse 511h – Temporisation 'Pénal'

#### \* Ecriture adresse 512h – Validation 0WS

D1 à D7 ...... Non significatifs

#### \* Lecture adresse 513h – Page logique bit A23

D1 à D7 ...... Non significatifs

#### \* Ecriture adresse 514h – Interruption carte vers PC

D1 à D7 ...... Non significatifs

#### \* Lecture adresses 516h à 519h et 51Ah- Compteur 32 bits à 100 us

516h

D0 à D7 du compteur

517h

D7 à D15 du compteur

518h

D16 à D23 du compteur

519h

D24 à D31 du compteur

Les adresses 516h à 519h permettent de lire la valeur d'un compteur 32 bits incrémenté toutes les 100 µs. Effectuer une première lecture a l'adresse 51Ah, puis lire successivement 516h, 517h, 518h et 519h. Ce compteur est remis à 0 après un reset de la carte.

#### B.2 ADRESSAGE DES REGISTRES DE L'EXTENSION PCB570-X

Notez qu'il est indispensable de disposer de la documentation « HITACHI HD64570 SCA user's manual » pour programmer la carte d'extension.

Les cartes PCB/570-2, PCB570-4 comprennent un ou deux contrôleurs de communication HITACHI HD64570-16 (oscillateur 16 MHz). La structure générale d'un contrôleur est la suivante :

- 2 voies série

- 4 canaux DMA (2 en écriture et 2 en lecture)

- 4 timers

Toutes les registres documentés dans ce paragraphe sont dans le plan d'adressage mémoire interne à la carte MCXCPCI/570-X.

#### - BF00:0 Adresses mémoires du contrôleur de communication n°1 des voies 1 et 2

```

BF00:0000 à BF00:001F registres généraux du contrôleur de communication registres de la voie série 1 registres de la voie série 2 registres des timers 1 à 4 registres des contrôleurs DMA 1 à 4

```

# - BF10:0 Adresses mémoires du contrôleur de communication n°2 des voies 3 et 4

```

BF10:0000 à BF10:001F registres généraux du contrôleur de communication registres de la voie série 3

BF10:0040 à BF10:005F registres de la voie série 4

BF10:0060 à BF10:007F registres des timers 1 à 4

BF10:0080 à BF10:00FF registres des contrôleurs DMA 1 à 4

```

# - BF80:0 Adresses mémoires du contrôleur de communication n°3 des voies 5 et 6

```

BF80:0000 à BF80:001F registres généraux du contrôleur de communication registres de la voie série 5

BF80:0040 à BF80:005F registres de la voie série 6

BF80:0060 à BF80:007F registres des timers 1 à 4

BF80:0080 à BF80:00FF registres des contrôleurs DMA 1 à 4

```

# - BF90:0 Adresses mémoires du contrôleur de communication n°4 des voies 7 et 8

| BF90:0000 à BF90:001F | registres généraux du contrôleur de communication |

|-----------------------|---------------------------------------------------|

| BF90:0020 à BF90:003F | registres de la voie série 7                      |

| BF90:0040 à BF90:005F | registres de la voie série 8                      |

| BF90:0060 à BF90:007F | registres des timers 1 à 4                        |

| BF90:0080 à BF90:00FF | registres des contrôleurs DMA 1 à 4               |

- Adresse mémoire BF20:0 en écriture : Direction horloge transmission et contrôle DTR pour voies 1 à 4.

- Adresse mémoire BFA0:0 en écriture : Direction horloge transmission et contrôle DTR pour voies 5 à 8.

TxCLK sortant : Horloge de transmission sortante et disponible sur la paire TxClkOut

TxCLK entrant : Horloge de transmission entrante sur la paire TxClkIn

| D0 Direction he | orloge de transmission voie 1/5 |

|-----------------|---------------------------------|

| D0 = 0          | Sortante                        |

| D0 = 1          | Entrante                        |

| D1 Direction he | orloge de transmission voie 2/6 |

| D1 = 0          |                                 |

| D1 = 1          |                                 |

| D2 Direction he | orloge de transmission voie 3/7 |

| D2 = 0          |                                 |

| D2 = 1          | Entrante                        |

| D3 Direction he | orloge de transmission voie 4/8 |

| D3 = 0          |                                 |

| D3 = 1          |                                 |

| D4 Contrôle sig | gnal DTR voie 1/5               |